# ガスソース MBE による高歪み Ge チャネル高速デバイス開発

# 研究代表者 武蔵工業大学・総合研究所・澤野憲太郎

## 研究分担者名

武蔵工業大学・総合研究所・星 裕介、佐藤 雄、平岡 良康 東北大学・金属材料研究所・宇佐美 徳隆、中嶋 一雄

## 1. はじめに

シリコンLSI技術は、今日の高度情報化社会を支えていると言っても過言ではなく、そのこれまでの発展は、素子サイズの縮小化による高集積化と高速化によって達成されてきた。しかし近年、Si-MOSFET において微細化による性能向上に限界が訪れている。この問題を打破するため、チャネルのキャリア移動度を向上させる技術が現在盛んに研究されている。その中で我々は、本質的にSiよりも移動度が高く、かつSiと化学的性質が類似しているGeをチャネル材料として導入することを試みた。そして、更に歪みを印加して「歪みGeチャネル」とすることで、飛躍的な移動度増大の実現を目指した。「歪み」の導入により、結晶の対称性低下によるバンド間散乱の低減や、有効質量の減少効果などにより、大幅な移動度増大が期待される。

Si と Ge は格子不整合が大きい(4.2%)ため、通常、Si 基板上に、Si Ge 緩和バッファー層(Si Ge 擬似基板)を介して、圧縮歪み Ge 層が形成される。ここで、高移動度の Ge チャネルを実現するためには、可能な限り大きな歪みを有する Ge 層を形成することが重要であると考えられる。そこで本研究では、「歪み Ge/低 Ge 組成 Si Ge 擬似基板」構造の高速デバイス開発を目的とする。擬似基板自体の作製の容易さ、プロセス、デバイス特性などの点からも、Si Ge 擬似基板の Ge 組成は薄く、つまり Si により近い方が好ましく、本研究のターゲットはまさにデバイス応用に直結する構造である。

歪みの大きなGe層の成長には、その歪み緩和を抑制するために、300~400℃という比較的低温での非平衡 状態での成長が不可欠である。そのため、低温成長が容易に行える、固体ソース分子線エピタキシー法(SS MBE)が主に利用され、高移動度が記録されている。しかしながら、SSMBEは量産に不適切であるという欠 点がある。また、固体ソース成長に由来する結晶欠陥の存在により、バッファー層に多くの正孔が発生してし まう。これは、パラレル伝導として移動度を大きく低減させるばかりでなく、オフリーク電流としてデバイス 動作に大きな悪影響をもたらす。そこで本研究では、ガスソース(GS)MBEを用いたGeチャネル構造を実現す ることを目的とした。

## 2. 研究経過

上記の目的に基づき、まずGSMBEによるSiGe擬似基板開発を進めた。ここでキーテクノロジーとなるのは、 我々が独自に開発してきている「イオン注入法」の適用である。これは、SSMBEを用いた擬似基板形成手法 として確立されている、いわゆる「低温バッファー法」に代わる手法である。低温バッファー法は、低温成長 により生じる欠陥を、バッファー層高品質化に積極的に利用する手法であるが、GSMBE法では適用できない。 イオン注入法は、イオン注入により欠陥を導入することで、低温法と類似の効果をGSMBE成長においても発 現させることが期待できる。つまり、GSMBEとイオン注入法を駆使して高品質SiGe擬似基板開発を行った上 で、その基板上に高歪みGeチャネル構造を形成し、その電気伝導特性を評価した。

研究体制としては、ガスソース MBE による結晶成長を東北大学で行い、 その他のデバイス作製プロセス、ホール測定、AFM、TEM 評価を武蔵工 業大学で行った。

## 3. 研究成果

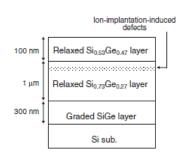

本研究で開発した、SiGe擬似基板の具体的な形成手法について以下に述べる(図 1)。まずGSMBEにより、Si基板上にSi<sub>0.73</sub>Ge<sub>0.27</sub>バッファー層を成長する。ここでGe組成を傾斜的に27%まで上昇させる傾斜組成法を用いた。そのバッファー層表面に、Siイオンを25 keV、 $5\times10^{15}$  cm<sup>-2</sup> でイオン注入し欠陥を導入した。その後、成長温度500 °Cで、Ge組成47%、

図1 SiGe 擬似基板構造図

膜厚100 nmのSi<sub>0.53</sub>Ge<sub>0.47</sub>層を成長させ、窒素雰囲気中で900 °C、1時間熱処理を行うことで緩和を促進させた。なおこの膜厚は従来法に比べて一桁程度小さいものである。

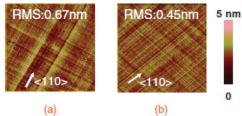

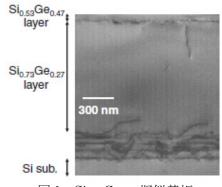

図 2 に作製した試料の表面AFM像を示す。参照用の、イオン注入を施していない試料に比べ、RMSラフネスが低く抑えられ、0.45 nmと非常に平坦なSiGeバッファー層が形成できていることが示された。これは、イオン注入により、転位源となる欠陥が均一に導入されることで、Sio.53Geo.47/Sio.73Geo.27 界面でミスフィット転位が均一に生じたことによると考えられる。なお、一般に報告されているSiGeバッファー層(Ge ~50%)の表面ラフネスは10 nm程度以上の大きさであり、本研究の手法によって一桁以上も平坦化が達成されている。図 3 に作製試料の断面TEM像を示す。多くの転位はSio.53Geo.47/Sio.73Geo.27 界面およびSi/Sio.73Geo.27 界面に集中しており、最表面まで達する貫通転位の少ない、高品質な膜が形成されていることが分かる。

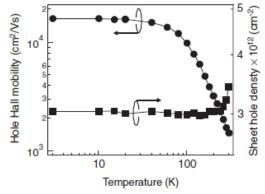

この構造に歪みGeチャネル構造を固体ソースMBE法によって 再成長し、ホール測定によってその電気伝導特性を調べた。図 4に正孔移動度と正孔濃度の温度依存性を示す。低温で16500 cm²/Vs、室温で1450 cm²/Vsという非常に高い移動度が得られて いる。これは、これまでに固体ソースMBEによる低温バッファーを用いて得られている値に匹敵し、Si-pMOSの10倍以上の値 であり、ガスソースMBE成長とイオン注入法を導入した本手法 が非常に有望であることを示している。なお、低温バッファーを用いた場合、低温成長特有のp-likeな欠陥の発生によって、室 温領域で正孔濃度が数倍に上昇してしまうことが分かってい るが、本試料においは、ガスソース成長の結晶高品質化の 効果で、その上昇率は極めて小さく、デバイス動作の弊害 となるパラレル伝導が大幅に抑制できることを示している。

さらに、SiGe 擬似基板とともに Ge チャネル層のガスソース成長を試み、成長温度の低温化によって従来法に比較して 2 倍近く大きな歪みを有する歪み Ge チャネルの形成に成功している。これによって、これまで以上に高品質な結晶性を有する Ge チャネル層が形成され、今後のデバイス高速化が非常に期待される。

また、イオン注入法を応用した、選択的欠陥導入技術の開発も進め、より高い移動度につながるものとして期待されている、面内で非対称な一軸性歪み Si/Ge ヘテロ構造の形成にも成功した。これは、上記の Ge チャネルとの組み合わせによって、今後さらなる高移動度化に結びつくものと期待できる。

図 2 Si<sub>0.53</sub>Ge<sub>0.47</sub>層表面の AFM 像。(a)は イオン注入なし、(b)はイオン注入あり。

図 3 Si<sub>0.53</sub>Ge<sub>0.47</sub>擬似基板 の断面 TEM 像

図 4 歪み Ge チャネル構造における 正孔 と正孔濃度の温度特性

### 4. まとめ

高速 Ge チャネルデバイスの実現へ向けて、ガスソース MBE とイオン注入法によって高品質 SiGe 擬似基板の開発を行い、その上へ高歪み Ge チャネル構造を形成し、電気伝導特性評価を行った。イオン注入法の効果によって、表面が非常に平坦で、かつ低転位密度の SiGe 擬似基板の形成に成功し、Si の 10 倍を超える高移動度を得ることができた。

# 非晶質基板上への多結晶 Si の形成における核形成制御

山梨大学・医学工学総合研究部・有元圭介

東北大学・金属材料研究所・中嶋一雄、宇佐美徳隆

### 1. はじめに

非晶質  $SiO_2$  上への多結晶半導体薄膜の形成は、画像表示装置や非晶質基板への回路形成等に応用され、低温プロセスで良質な結晶を得ることが要求されている。特に、有機 EL など電流駆動表示素子用には移動度が低く抵抗が大きいアモルファス Si から低抵抗の多結晶 Si への置き換えが進んでいる。現在、多結晶 Si 薄膜の作製には、アモルファス Si 膜をエキシマ・レーザー・アニールで溶融・結晶化させる手法が用いられている。この従来の方法では、核形成の制御が難しく、結晶性の向上や配向の制御は限界に近付いている。そこで我々は、固相結晶化および気相成長における核形成過程の制御を可能にする新しい手法を開発し、結晶性・配向性の制御を目指して研究を行っている。

#### 2. 研究経過

パターニングが固相結晶化過程に及ぼす影響について調べるため、2種類の実験を行った。1つ目の実験では、石英基板上にアモルファス Si を成膜し、細線状に加工した後に熱処理を行い、固相結晶化過程の観察を行った。2つ目の実験では、異方性エッチングを用いて V 溝状に加工した Si(001)基板を熱酸化し、その上にアモルファス Si を成膜し、固相結晶化過程を観察した。観察手法として、走査透過型電子顕微鏡による観察および顕微ラマンマッピング測定を行い、結晶化の過程を調べた。

### 3. 研究成果

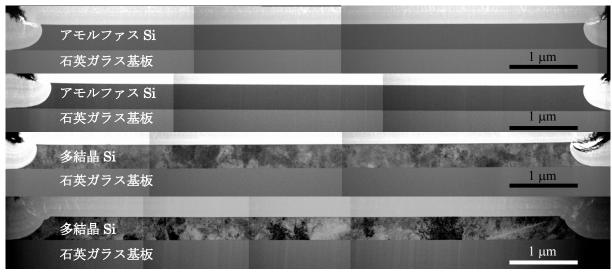

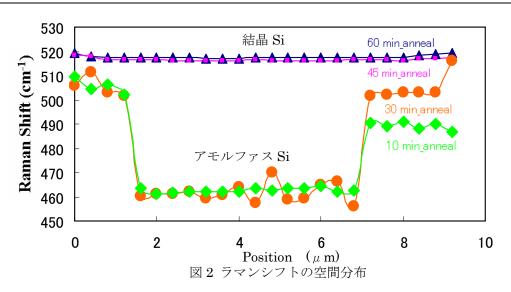

1つ目の実験ではアモルファス Si 薄膜をドライエッチングにより細線状に加工した後に熱処理を行い、結晶化過程を調べた。図 1 は窒素雰囲気下  $700^{\circ}$ Cでそれぞれ 10 分・30 分・45 分・60 分間アニールした試料の断面 STEM 像である。30 分から 45 分の間に急速に結晶化が進んでいる。各試料の顕微ラマン分光測定の結果を図 2 に示す。アニール時間が 10 分・30 分の試料でも、端部では結晶性のピークが見られた。ラマンシフトの値から、この状態では微結晶が形成されていると考えられる(高分解能 TEM による観察も行ったが、端部において結晶性の領域を確認することはできなかった)。中心部分で結晶化が相対的に遅いことから、この構造では表面近傍が一様に核形成サイトになっている訳ではなく、細線端部が他の表面とは異なる性質を持っていることが分かる。現時点では、応力についての拘束条件が部位によって異なり、結晶化の結果生じる歪みエネルギーが端部と他の部位で異なるためではないかと考えている。

図1 STEM 像

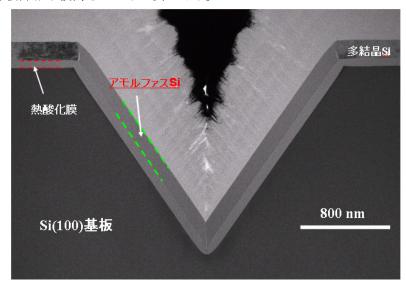

次に、2つ目の実験の結果を示す。図 3 は、V 溝状に加工した Si を熱酸化し、その上にアモルファス Si を堆積し、670  $\mathbb C$   $\mathbb C$  1 時間熱処理を施した試料の断面 STEM 像である。V 溝の上部ではこの条件で固相結晶化が起こっている。一方、斜面では結晶化が全く起きていない。別の実験から、この違いは温度の空間分布によるものではないことも分かった。斜面部では、700  $\mathbb C$  · 10 時間のアニール後もなおアモルファス状態であった。この原因として、部位による応力条件の違い、アモルファス膜の形成過程において、膜質が部位によって微妙に異なる可能性などが考えられる。上部の多結晶化する領域の存在が斜面部の結晶化にどのように影響を及ぼしているか、今後詳細な検討を加える必要がある。

図3 断面STEM像

## 4. まとめ

石英基板上のアモルファス Si 細線、および V 溝熱酸化 Si 基板上のアモルファス Si 膜の固相成長に関して、結晶化が一様ではなく、部位によって結晶化のしやすさが異なることを見出した。詳細なメカニズムについては今後精査していく予定である。

# 電子スピン共鳴による I-III-VI。族化合物半導体の欠陥構造の解明

研究代表者名 都城高専・電気情報工学科・赤木洋二

研究分担者名 東北大学・金属材料研究所・米永一郎、大野裕

### 1. はじめに

近年、太陽電池用材料として薄膜系で世界最高の効率(20.0%)を誇るカルコパイライト構造をもつ I-III-VI2族化合物半導体が注目されている。しかしながら、太陽電池の変換効率は、ここ数年、最高効率はほとんど更新されず、その大きな理由の一つとしては、吸収層に存在する欠陥種の同定や格子欠陥の構造が十分解明されていないことが考えられる。従って、それらの解明は、変換効率の向上に大きく貢献すると考える。

本研究では、カルコパイライト型化合物半導体の多結晶バルクおよび薄膜を用いて、電子スピン共鳴 (ESR)により、格子欠陥の同定と構造を明らかにすることを目的とする。さらに、フォトルミネッセンス法やホール測定などの光学的、電気的特性のデータとも比較・対照し、欠陥種の同定を行う。また、太陽電池の作製も試み、格子欠陥と変換効率との関係についても調べる。

### 2. 研究経過

結晶はホットプレス法により育成した。これまでに I/III 族元素比を変数とした無添加および鉄族元素添加  $CuInS_2$  バルク (15 種類) と  $AgInS_2$  バルク (15 種類)、Mn 添加量を変数とした  $AgInS_2$  バルク (3 種類)、 $AgGaSe_2$  バルク (3 種類)の計 36 種類のサンプルと、別途真空蒸着法により作製した  $CuInS_2$  薄膜 (3 種類)の合計 39 種類について ESR 測定を行ってきた。特に、I/III 族元素比を変数とした  $EuInS_2$  バルク (5 種類)と  $EuInS_2$  バルク (3 種類)、鉄族元素を添加した  $EuInS_2$  バルク (5 種類)については低温での測定を行った。

### 3. 研究成果

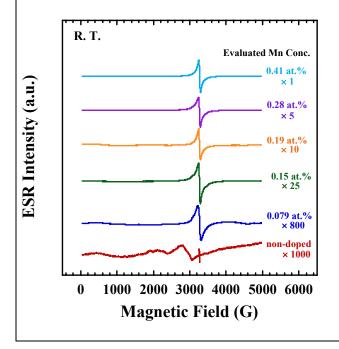

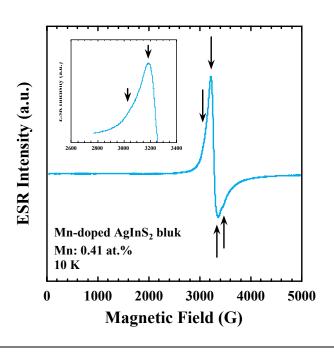

Mn を添加した  $AgInS_2$ バルク試料では室温において明確な ESR 信号が得られ、その強度は Mn 添加濃度の増加とともに大きくなった(図 1)。このとき、g 値は 1.98 となった。これらのサンプルは p 型であったことから、その成因として In サイトに置換した Mn 原子による欠陥  $(Mn_{In})$  の可能性が考えられる。また、Mn を 0.41 at. %添加した  $AgInSe_2$  バルクの 10 K における ESR 信号からは、ハイパーファイン信号は明確には観測されなかった。Mn を添加した ZnO 結晶や ZnS 薄膜などからも同様な ESR 信号が得られていることから、Mn の添加濃度が高すぎたことが理由の一つとして考えられる。鉄族元素を添加した  $CuInS_2$  バルクから得られた ESR 信号からは、複数のピークが観測されており、その詳細の検討を進めている。

## 先端シリコン材料の構造解析と機能評価

物質・材料研究機構・MANA・深田直樹、陳君 物質・材料研究機構・半導体材料センター・陳斌、李雄、王彦

> 研究分担者名 東北大学・金属材料研究所・伊藤 俊、高田九二雄

#### 1. はじめに

シリコンは、半導体産業を支える基盤材料であるが、近年の加工技術の発展により、将来の可能性が大きく広がっている。シリコンナノ材料は、2010年以降の新奇電子デバイスとして研究が行われている。シリコン材料の構造と機能の評価は、上記技術の発展には必要不可欠のものであるが、対象がナノサイズになると、適当な評価方法が開発されていない。本研究では、多様なシリコン材料を的確に評価する技術を確立することを目的として、電子顕微鏡による構造解析と、電子線誘起電流による電気的機能評価を組み合わせて、現実の材料を評価する。さらに格子欠陥の発生や増殖を制御するための、材料開発の指針を得る。

#### 2. 研究経過

物材機構において、減圧CVD法により、Auを触媒として、Siナノワイヤーを成長させた。さらに、B, Pを添加させてドーピングを行った。この試料の電気的特性を、ラマン散乱、電子スピン共鳴(ESR)法を用いて、Siナノワイヤーへのドーピング量を電気的に評価した。金研分析コアでは、透過電子顕微鏡を用いてナノワイヤーの構造や格子欠陥の観察を行った。また、シリサイドの形成過程を調べることを将来の目的とし、多結晶Siの結晶粒界に偏析したFeを、HAADF法によって調べた。

## 3. 研究成果

シリサイドの研究では、 $\Sigma 3\{112\}$ 粒界に偏析したFe不純物を、HAADF-STEMによって観察することに成功した。Siナノワイヤーの研究では、TEM観察、EDX、ESR、ラマン散乱測定等を行った。TEM観察の結果では、ナノワイヤーの表面は酸化膜で覆われており、全体径は約30-50nmで結晶コアの径は約10-20nmであることがわかった。PをドープしたSiナノワイヤーのEDXの分析では、PK $\alpha$ 線を観測することができた。ESR測定では、g値1.998のP伝導電子のシグナルを観測することに成功した。また、BをドープしたSiナノワイヤーのラマン散乱測定の結果では、Bの局在振動ピーク、およびFano効果によるSi光学フォノンピークのブロードニングを初めて観測することができた。以上の結果より、ドーパントであるBおよびP原子がSiナノワイヤー中の結晶コア内のSi置換位置に、電気的に活性な状態でドープされたことを証明できた。Siナノワイヤー中にドープされたPおよびB濃度は10<sup>19</sup>-10<sup>20</sup>cm<sup>-3</sup>台に達していると推測される。

#### 4. まとめ

本年度の第一の成果として、HAADF-STEM により $\Sigma$ 3{112}粒界に偏析した Fe 不純物を観察することに成功した。また、Si ナノワイヤーの構造およびドーピングを TEM 観察、EDX により明らかに出来た。ドーピングに関しては、ESR およびラマン散乱測定を行うことにより、P 伝導電子のシグナル、B の局在振動ピーク、および Fano 効果による Si 光学フォノンピークのブロードニングを初めて観測することができた。以上の結果により、n 型および p 型 Si ナノワイヤーの生成を証明できた。